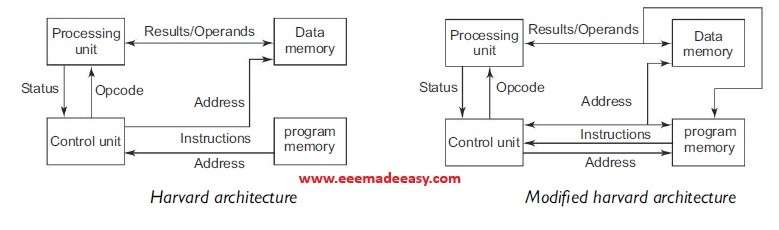

Modified Harvard Architecture: One of the ways by which the number of clock cycles required for the memory access can be reduced is to use more than one bus for both address and data. In the modified Harvard Architecture, One set of buses is used to access a memory that has both program and data, and another that has data alone. Data can also be transferred from one memory to another.

Digital Signal Processors, by B. Venkataramani

Join EEE Made Easy Whatsapp Channel

In the Harvard architecture shown in Fig. there are two separate buses for the program and data memory. Hence, the content of program memory and data memory can be accessed in parallel. The instruction code can be fed from the program memory to the control unit while the operand is fed to the processing unit from the data memory.

The processing unit, consisting of the registers and processing elements such as MAC units, multiplier, ALU, shifter, etc., are also referred to as the data path.

Join EEE Made Easy Telegram channel

Modified Harvard Architecture

The P-DSPs follow the modified Harvard architecture shown in the above Fig.

One set of buses is used to access a memory that has both program and data, and another that has data alone. Data can also be transferred from one memory to another.

The modified Harvard architecture is used in several P-DSPs, for example, P-DSPs from Texas Instruments and Analog Devices.

With the Harvard architecture, the number of memory accesses/clock cycle was shown to be two.

This can be increased further by using a larger number of buses.

For example, by using three separate address and data buses, the number of memory accesses/clock cycle can be increased to three.

Motorola DSP5600X, DSP96002, etc. have three separate buses. TMS320C54X has four address buses.

Since the cost of an IC increases with the number of pins in the IC, extending a number of buses outside

the chip would unduly increase the price.

Hence, the P-DSP’s use multiple buses only for connecting the on-chip memory to the control unit and data path. For accessing off-chip memory, only a single bus is used for accessing both the program memory and data memory. Because of this, any operation that involves an off-chip memory is slow compared to that using the on-chip memory.

Read also: TMS320C5X Architecture

Book for Digital Signal Processor

Digital Signal Processors, by B. Venkataramani

Join EEE Made Easy Whatsapp Channel

Download EEE Made Easy Ebook PDF Free

Latest Posts in EEE Made Easy

- Compensating WindingsCompensating Windings: Compensating Windings are used for large direct current machines which are subjected to large fluctuations in load i.e. … Read more

- Transformers Electrical Engineering Interview QuestionsTransformers Electrical Engineering Interview Questions: QUESTIONS AND ANSWERS ON TRANSFORMERS Read: 125 Electrical Interview Questions Q.1. How is magnetic leakage … Read more

- DC Motor Electrical Engineering Interview QuestionsDC Motor Electrical Engineering Interview Questions: DC Motor Interview Questions and answers. Read: 125 Electrical Interview Questions Q. 1. How … Read more

- Special Electrical Machines Interview QuestionsSpecial Electrical Machines Interview Questions: Electrical Interview Questions Read: Electrical Interview Q.1. Do stepper motors have internal or external fans? … Read more

- 125 Electrical Engineering Interview QuestionsElectrical Engineering Interview Questions: Read 125 Questions based on Electrical Interview Questions. 1) What is Electrical Engineering? Electrical Engineering … Read more

- Syllabus Training Instructor Plumber|14/2025 Syllabus Kerala PSCSyllabus Training Instructor Plumber: 14/2025 Syllabus Kerala PSC. Download the syllabus and Previous question papers for the Training Instructor in … Read more

- [PDF] Syllabus AE KSEB Transfer|378/2025 Syllabus Kerala PSCSyllabus AE KSEB Transfer: DETAILED SYLLABUS FOR THE POST OF ASSISTANT ENGINEER(ELECTRICAL) (Kerala State Electricity Board Ltd.) – By Transfer … Read more